集成電路設(shè)計,作為現(xiàn)代信息產(chǎn)業(yè)的核心與基石,是一門將電路系統(tǒng)、電子元件及其互連關(guān)系集成到一塊微小半導(dǎo)體芯片上的科學(xué)與藝術(shù)。它不僅是技術(shù)進(jìn)步的驅(qū)動力,更是數(shù)字時代得以實(shí)現(xiàn)的物理載體。

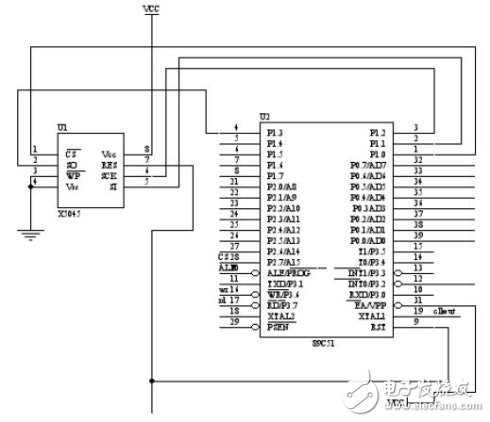

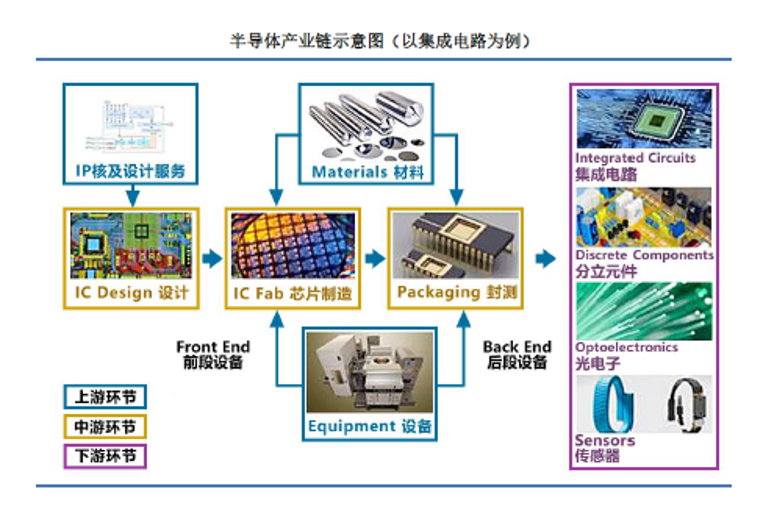

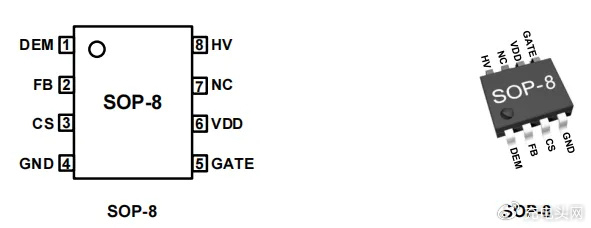

集成電路設(shè)計通常分為幾個關(guān)鍵階段。首先是系統(tǒng)架構(gòu)設(shè)計,工程師需要根據(jù)芯片的功能需求,規(guī)劃整體框架,確定模塊劃分和數(shù)據(jù)流。緊隨其后的是前端設(shè)計,包括使用硬件描述語言(如Verilog或VHDL)進(jìn)行邏輯設(shè)計、功能仿真和驗(yàn)證,確保邏輯功能的正確性。然后是后端設(shè)計,這是將邏輯門電路轉(zhuǎn)換為實(shí)際物理布局的過程,涉及布局規(guī)劃、時鐘樹綜合、布線與物理驗(yàn)證,需要在性能、功耗和面積之間做出精妙權(quán)衡。設(shè)計數(shù)據(jù)被送至晶圓廠進(jìn)行制造,流片成功后經(jīng)過封裝測試,一顆芯片才得以誕生。

當(dāng)前,集成電路設(shè)計正面臨多重挑戰(zhàn)與機(jī)遇。隨著工藝節(jié)點(diǎn)不斷微縮至納米級甚至更小,物理效應(yīng)(如量子隧穿、寄生效應(yīng))帶來的設(shè)計復(fù)雜性急劇增加。對低功耗(特別是移動與物聯(lián)網(wǎng)設(shè)備)、高性能計算(如人工智能與數(shù)據(jù)中心)以及高可靠性的需求日益迫切。這推動了設(shè)計方法與工具的革新,例如高層次綜合、基于機(jī)器學(xué)習(xí)的設(shè)計自動化、以及面向特定領(lǐng)域(如AI加速器)的架構(gòu)設(shè)計。

集成電路設(shè)計將持續(xù)向三維集成、異質(zhì)集成、光電子集成等方向發(fā)展。它不僅關(guān)乎單一芯片的性能,更關(guān)乎如何構(gòu)建高效、智能的系統(tǒng)。可以說,每一次智能設(shè)備的升級、每一輪科技浪潮的涌現(xiàn),背后都離不開集成電路設(shè)計師們在方寸之間進(jìn)行的精密構(gòu)思與創(chuàng)新。這門深奧的技術(shù),正悄然塑造著我們世界的模樣。